# MX554ENL120M000

#### Ultra-Low Jitter 120MHz LVPECL XO

#### ClockWorks® FUSION

## **General Description**

The MX554ENL120M000 is an ultra-low phase jitter XO with LVPECL output optimized for high line rate applications.

### Features

- 120MHz LVPECL

- Typical phase noise:

- 100fs (Integration range: 1.875MHz-20MHz)

- ±50ppm total frequency stability

- $-40^{\circ}$ C to  $+85^{\circ}$ C temperature range

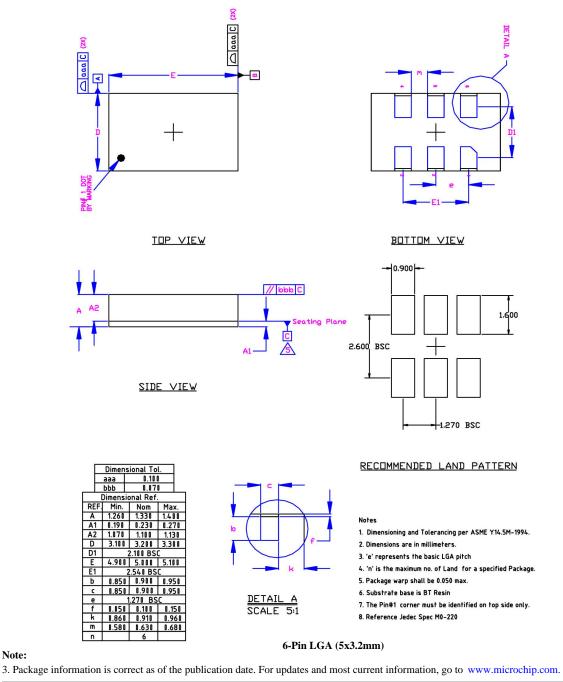

- Industry standard 6-Pin 5mm x 3.2mm LGA package

## **Absolute Maximum Ratings**

| Supply Voltage (VIN)                  | +4.6V |

|---------------------------------------|-------|

| Lead Temperature (soldering, 10s)     |       |

| Storage Temperature (T <sub>s</sub> ) | 125°C |

| ESD Rating (HBM)                      |       |

## **Electrical Characteristics**

VDD = 2.375 - 3.63V, TA =  $-40^{\circ}C$  to  $+85^{\circ}C$ , outputs terminated with 50 Ohms to VDD -  $2V.^{1}$

| Symbol | Parameter                            | Condition                                                                   | Min.       | Тур.       | Max.      | Units |

|--------|--------------------------------------|-----------------------------------------------------------------------------|------------|------------|-----------|-------|

| IDD    | Supply Current                       |                                                                             |            |            | 120       | mA    |

| F0     | Center Frequency                     |                                                                             |            | 120        |           | MHz   |

|        | Frequency Stability                  | Note 2                                                                      |            |            | ±50       | ppm   |

| Øj     | Phase Noise                          | Integration Range (12kHz to 20MHz)<br>Integration Range (1.875MHz to 20MHz) |            | 220<br>100 |           | fsRMS |

| Tstart | Start-Up Time                        |                                                                             |            |            | 20        | ms    |

| TR/TF  | Rise/Fall time                       |                                                                             | 85         |            | 350       | ps    |

|        | Duty Cycle                           |                                                                             | 45         |            | 55        | %     |

| VOH    | Output High Voltage                  | LVPECL output levels                                                        | VDD - 1.35 | VDD - 1.01 | VDD - 0.8 | V     |

| VOL    | Output Low Voltage                   | LVPECL output levels                                                        | VDD - 2.0  | VDD - 1.78 | VDD - 1.6 | V     |

| Vswing | Peak to Peak Output<br>Voltage Swing |                                                                             | 0.65       | 0.77       | 0.95      | v     |

Notes:

1. Guaranteed after thermal equilibrium.

2. Inclusive of initial accuracy, temperature drift, aging, shock, vibration.

ClockWorks is a registered trademark of Microchip Technology Inc.

Microchip Technology Inc.

March 16, 2017 MX554EN2-4994 http://www.microchip.com

Revision 1.0 tcghelp@microchip.com

## **Operating Ratings**

Supply Voltage (VIN).....+2.375V to +3.63V Ambient Temperature (TA)....-40°C to +85°C

# **Ordering Information**

| Ordering Part Number | Marking Line 1 | Marking Line 3 | Shipping      | Package               |

|----------------------|----------------|----------------|---------------|-----------------------|

| MX554ENL120M000      | MX554E         | NL1200         | Tube          | 6-Pin 5mm x 3.2mm LGA |

| MX554ENL120M000 TR   | MX554E         | NL1200         | Tape and Reel | 6-Pin 5mm x 3.2mm LGA |

Devices are Green and RoHS compliant. Sample material may have only a partial top mark.

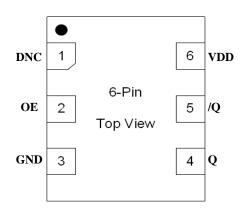

# **Pin Configuration**

# **Pin Description**

| Pin Number | Pin Name | Pin Type | Pin Level | Pin Function                                                                                  |

|------------|----------|----------|-----------|-----------------------------------------------------------------------------------------------|

| 1          | DNC      |          |           | Make no connection, leave floating.                                                           |

| 2          | OE       | I, SE    | LVCMOS    | Output Enable, disables output to tri-state,<br>1 = Disabled, 0 = Enabled, 50k Ohms Pull-Down |

| 3          | GND      | PWR      |           | Power Supply Ground                                                                           |

| 4, 5       | Q, /Q    | O, Diff  | LVPECL    | Clock Output Frequency = 120MHz                                                               |

| 6          | VDD      | PWR      |           | Power Supply                                                                                  |

#### Package Information and Recommended Land Pattern for 6-Pin LGA<sup>3</sup>

#### Microchip Technology Inc.

#### http://www.microchip.com

Microchip makes no representations or warranties with respect to the accuracy or completeness of the information furnished in this data sheet. This information is not intended as a warranty and Microchip does not assume responsibility for its use. Microchip reserves the right to change circuitry, specifications and descriptions at any time without notice. No license, whether express, implied, arising by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Microchip's terms and conditions of sale for such products, Microchip assumes no liability whatsoever, and Microchip disclaims any express or implied warranty relating to the sale and/or use of Microchip products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right.

© 2017 Microchip Technology Inc.

Note: